### (19) United States

# (12) Patent Application Publication (10) Pub. No.: US 2018/0138215 A1

May 17, 2018 (43) **Pub. Date:**

#### (54) DISPLAY DEVICE AND METHOD FOR DRIVING THE SAME

(71) Applicant: Semiconductor Energy Laboratory Co., Ltd., Atsugi-shi (JP)

(72) Inventor: Hajime KIMURA, Kanagawa (JP)

Appl. No.: 15/814,521 (21)

(22)Filed: Nov. 16, 2017

#### Related U.S. Application Data

(63) Continuation of application No. 13/855,753, filed on Apr. 3, 2013, now Pat. No. 9,825,068, which is a continuation of application No. 13/555,247, filed on Jul. 23, 2012, now Pat. No. 8,508,443, which is a continuation of application No. 10/291,736, filed on Nov. 12, 2002, now Pat. No. 8,242,986.

#### (30)Foreign Application Priority Data

Nov. 13, 2001 (JP) ...... 2001-348032

#### **Publication Classification**

| (51) | Int. Cl.    |           |

|------|-------------|-----------|

|      | H01L 27/12  | (2006.01) |

|      | G09G 3/3291 | (2016.01) |

|      | G09G 3/3233 | (2016.01) |

|      | G09G 3/3266 | (2016.01) |

|      | G09G 3/20   | (2006.01) |

H04W 52/02 (2009.01)H01L 27/32 (2006.01)

U.S. Cl.

CPC ...... H01L 27/1255 (2013.01); H01L 27/3244 (2013.01); G09G 3/3233 (2013.01); G09G *3/3266* (2013.01); *G09G 2330/08* (2013.01); G09G 2320/043 (2013.01); G09G 2310/061 (2013.01); G09G 2310/027 (2013.01); G09G 2310/0256 (2013.01); G09G 2310/0251 (2013.01); G09G 2300/0842 (2013.01); G09G 2300/0426 (2013.01); G09G 3/2022 (2013.01); G09G 2330/10 (2013.01); Y02D 70/00 (2018.01); H04W 52/027 (2013.01); G09G 3/3291 (2013.01)

#### (57)ABSTRACT

A semiconductor device having a configuration hardly generating variations in the current value due to a deteriorated EL element is to be provided. A capacitance element is disposed between the gate and the source of a driving TFT, video signals are inputted to the gate electrode, and then it is in the floating state. Suppose an EL element is deteriorated and the anode potential rises, that is, the source potential of the driving TFT rises, the potential of the gate electrode of the driving TFT, being in the floating state by coupling of the capacitance element, is to rise by the same amount. Accordingly, even when the anode potential rises due to the deteriorated EL element, the rise is added to the gate electrode potential as it is, and the gate-source voltage of the driving TFT is allowed to be constant.

Fig. 2A

Fig. 2B

Fig. 2C

Fig. 2D

Fig. 30

Fig. 4A

Fig. 5A

Fig. 6A

Fig. 9

Fig. 10B

Fig. 11A

Fig. 110

Fig. 12D

Fig. 15C

Fig. 16B

Fig. 17A

Fig. 18B

1901 S-CLK S-CLKb FF S-SP Digital Data Latch Pulse Sn-1 Sn S  $S_2$ Sa S4 1902 1903

Fig. 19B

Fig. 21A

Fig. 21B

Fig. 21C

Fig. 22

# DISPLAY DEVICE AND METHOD FOR DRIVING THE SAME

# CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application is a continuation of U.S. application Ser. No. 13/855,753, filed Apr. 3, 2013, now allowed, which is a continuation of U.S. application Ser. No. 13/555, 247, filed Jul. 23, 2012, now U.S. Pat. No. 8,508,443, which is a continuation of U.S. application Ser. No. 10/291,736, filed Nov. 12, 2002, now U.S. Pat. No. 8,242,986, which claims the benefit of a foreign priority application filed in Japan as Serial No. 2001-348032 on Nov. 13, 2001, all of which are incorporated by reference.

#### BACKGROUND OF THE INVENTION

[0002] The present invention relates to the configuration of a semiconductor device having a transistor. The invention also relates to the configuration of an active matrix display device including a semiconductor device having a thin film transistor (hereafter, it is denoted by TFT) fabricated on an insulator such as glass and plastics. In addition, the invention relates to an electronic device using such the display device

[0003] In recent years, the development of display devices using light emitting elements including electroluminescent (EL) elements has been conducted actively. The light emitting element has high visibility because it emits light for itself. It does not need a back light that is needed in liquid crystal display devices (LCD), and thus it is suitable for forming to have a low profile and has nearly no limits to the field of view.

[0004] Here, the EL element is an element having a light emitting layer that can obtain luminescence generated by applying an electric filed. The light emitting layer has light emission (fluorescence) in returning from the singlet excited state to the ground state, and light emission (phosphorescence) in returning from the triplet excited state to the ground state. In the invention, the light emitting device may have any light emission forms above.

[0005] The EL element is configured in which the light emitting layer is sandwiched between a pair of electrodes (an anode and a cathode), forming a laminated structure in general. Typically, the laminated structure of the anode/hole transport layer/emissive layer/electron transport layer/cathode is named, which was proposed by Tang et al., Eastman Kodak Company. This structure has significantly high luminous efficiency, which is adapted to many EL elements now under investigation.

[0006] Furthermore, there are the other structures laminated between an anode and a cathode in the order of the hole injection layer/hole transport layer/light emitting layer/electron transport layer, or hole injection layer/hole transport layer/electron injection layer. As the EL element structure used for the light emitting device in the invention, any structure described above may be adapted. Moreover, fluorescent dyes may be doped into the light emitting layer.

[0007] In the specification, the entire layers disposed between the anode and the cathode are collectively called the EL layer in the EL element. Accordingly, the hole injection layer, the hole transport layer, the light emitting layer, the electron transport layer, and the electron injection

layer are all included in the EL element. The light emitting element formed of the anode, the EL layer, and the cathode is called EL element.

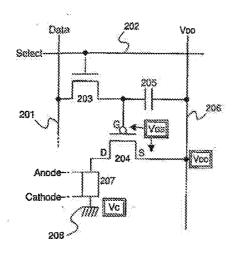

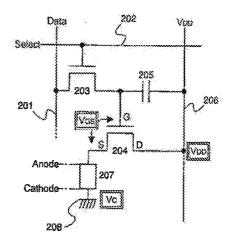

[0008] FIGS. 2A and 2B depict the configuration of a pixel in a general light emitting device. In addition, as the typical light emitting device, an EL display device is exemplified. The pixel shown in FIGS. 2A and 2B has a source signal line 201, a gate signal line 202, a switching TFT 203, a driving TFT 204, a capacitance element 205, a current supply line 206, an EL element 207, and a power source line 208. The P-channel type is used for the driving TIT 204 in FIG. 2A, and the N-channel type is used for the driving TFT 204 in FIG. 2B. The switching TFT 203 is a TFT that functions as a switch in inputting video signals to the pixel, and thus the polarity is not defined.

[0009] The connection of each part will be described. Here, the TFT has three terminals, the gate, the source and the drain, but the source and the drain cannot differ from each other distinctly because of the structure of the TFT. Therefore, in describing the connection between the elements, one of the source and the drain is denoted by a first electrode, and the other is a second electrode. When the description is needed for potential of each terminal (the gate-source voltage of a certain TFT) about turning on and off the TFT, the source and the drain are denoted.

[0010] Furthermore, in the specification, the TFT being on is the state that the gate-source voltage of the TFT exceeds the threshold and current is carried between the source and the drain. The TFT being off is the state that the gate-source voltage of the TFT drops below the threshold and current is not carried between the source and the drain.

[0011] The gate electrode of the switching TFT 203 is connected to the gate signal line 202, the first electrode of the switching TFT 203 is connected to the source signal line 201, and the second electrode of the switching TFT 203 is connected to the gate electrode of the TFT driving TFT 204. The first electrode of the driving TFT 204 is connected to the current supply line 206, and the second electrode of the driving TFT 204 is connected to the anode of the EL element 207. The cathode of the EL element 207 is connected to the power source line 208. The current supply line 206 and the power source line 208 have the potential difference each other. Moreover, to hold the gate-source voltage of the driving TFT 204, a certain fixed potential, the capacitance element 205 may be disposed between the gate electrode of the driving TFT 204 and the current supply line 206, for example.

[0012] When a pulse is inputted to the gate signal line 202 to turn on the switching TFT 203, video signals having been outputted to the source signal line 201 are inputted to the gate electrode of the driving TFT 204. The gate-source voltage of the driving TFT 204 is determined in accordance with the potential of the inputted video signals, and the current carried between the source and drain of the driving TFT 204 (hereafter, it is denoted by drain current) is determined. This current is supplied to the EL element 207 to emit light.

#### SUMMARY OF THE INVENTION

[0013] The display device in which TFTs are formed on a substrate and a pixel part and peripheral circuits are built in one piece is applied to mobile devices in significant growth, taking advantage of its small size and lightweight. At the same time, TFTs are formed through many processes such as

film deposition, device fabrication by repeating etching, and injection of impurity elements for giving conductivity to semiconductors, thus having a challenge of cost reduction by curtailing the processes.

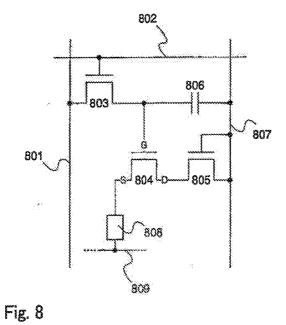

[0014] Then, when the pixel part and the peripheral circuits are configured of unipolar TFTs, a part of the process of injecting impurity elements can be omitted. As an example of a pixel formed by using unipolar TFTs, the pixel shown in FIG. 8 is proposed in *Amorphous Silicon Thin-Film Transistors Based Active-Matrix Organic Light-Emitting Displays ASIA DISPLAY*, page 315, (2001).

[0015] The pixel shown in FIG. 8 has a source signal line 801, a gate signal line 802, a switching TFT 803, a driving TFT 804, an active resistance TFT 805, a capacitance element 806, a current supply line 807, EL element 808, and a power source line 809, using the N-channel TFT for the TFTs 803 to 805.

[0016] The gate electrode of the switching TFT 803 is connected to the gate signal line 802, the first electrode of the switching TFT 803 is connected to the source signal line 801, and the second electrode of the switching TFT 803 is connected to the gate electrode of the driving TFT 804. The first electrode of the driving TFT 804 is connected to the anode of the EL element 808, and the second electrode of the driving TFT 804 is connected to the first electrode of the active resistance TFT 805. The gate electrode and the second electrode of the active resistance TFT 805 are connected each other, which are connected to the current supply line **807**. The cathode of the EL element **808** is connected to the power source line 809, having the potential difference with the current supply line 807 each other. The capacitance element 806 is disposed between the gate electrode of the driving TFT 804 and the current supply line 807, holding the potential of signals applied to the gate electrode of the driving TFT 804.

[0017] As shown in FIGS. 2A and 8, the operation of using the N-channel TFT for the driving TFT will be considered. FIG. 2C depicts only the configured portion of the current supply line 206 to the driving TFT 204 to the EL element 207 to the power source line 208 in the pixel shown in FIGS. 2A and 2B. The driving TFT 204 is formed to be the N-channel type, and thus one side connected to the anode of the EL element 207 is the source, and the other side connected to the current supply line is the drain.

[0018] Now, suppose the potential of the current supply line 206 is  $V_{DD}$ , the anode potential of the EL element 207 is  $V_A$ , the cathode potential thereof is  $V_C$ , and the potential of the gate electrode of the driving TFT 204 is  $V_{Sig}$ . The gate-source voltage  $V_{GS}$  of the driving TFT 204 is  $V_{GS}$ = ( $V_{Sig}$ - $V_A$ , and the anode-cathode voltage  $V_{EL}$  of the EL element 207 is  $V_{EL}$ =( $V_A$ - $V_C$ ).

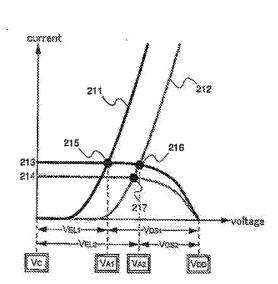

[0019] FIG. 2D depicts the voltage-current characteristics of the driving TFT 204 and the EL element 207. The intersection of the voltage-current curve of the driving TFT 204 and the voltage-current curve of the EL element 207 is the operating point, determining the current value carried through the EL element 207 and the anode potential  $V_A$  of the EL element. Now, when the voltage-current curve of the EL element 207 is expressed by 211 and the voltage-current curve of the TFT 204 is expressed by 213, the operating point falls into 215, whereby the current value and  $V_A = V_{A1}$  are determined. In addition, the gate-source voltage  $V_{GS}$  of the driving TFT 204 at this time is expressed by  $V_{GS} = V_{A1}$ .

[0020] Here, the case of the EL element 207 having been deteriorated will be considered. When the EL element 207 is deteriorated, the voltage to start lighting rises, the curve is shifted to the right and expressed by 212. Here, suppose the driving TFT 204 is operated in the saturation region and the deteriorated EL element 207 does not cause the gate-source voltage to be varied, the operating point shifts to 216. More specifically, it turns to be  $V_A = V_{A2}$ . In this case, even though the source-drain voltage of the driving TFT 204 is varied, the current value is not varied greatly, and thus the luminance is not varied so much. However, at present, the N-channel TFT is used for the driving TFT 204 and the one side connected to the anode of the EL element 207 is the source. Thus, the gate-source voltage  $\mathbf{V}_{GS}$  of the driving TFT  $\mathbf{204}$  becomes as small as  $V_{GS}=(V_{Sig}-V_{A2})$ . Therefore, the voltage-current curve of the driving TFT **204** at this time is expressed by 214. Accordingly, the operating point falls into 217. More specifically, the deteriorated EL element 207 caused the source potential of the driving TFT 204 to rise and the gate-source voltage to be small, and thus the current value is changed greatly, leading to the decrease in the luminance. [0021] In the invention, the object is to provide a semiconductor device, in which the N-channel TFT is used for the driving TFT for supplying current to the EL element, capable of solving the problems caused by the deteriorated EL element as described above.

[0022] The main point of the above-described object is the deteriorated EL element caused the anode potential of EL element, namely, the source potential of the driving TFT to rise and therefore the gate-source voltage of the driving TFT to be small.

[0023] In order to make the current value not to be varied when the EL element is deteriorated, it is necessary to make the gate-source voltage of the driving TFT not to be varied when the deteriorated EL element causes the anode potential of EL element to rise.

[0024] In the invention, a structure adopting a bootstrap operation is applied to the pixel. A capacitance element is provided between the gate and the source of the driving TFT, and the source potential is set to a certain value during a period that the image signals are inputted to the gate electrodes. After the image signals are inputted, the gate electrodes are in a floating state. At this time, if the sourcegate voltage of the driving TFT is in excess of the threshold value, the driving TFT is turned to ON. However, if the set source potential of the driving TFT is released, the current flows to the EL element, as a result, the anode potential, namely, the source potential of the driving TFT rises. Accordingly, the potential of the gate electrodes in a state of floating, by coupling of the capacitance element disposed between the gate and the source of the driving TFT, is to rise by the same amount. As a result, when the anode potential rises variously due to the deterioration of EL element, the rise can be added over to the potential of the gate electrodes as it is, and the gate-source voltage of the driving TFT is allowed to be constant thereby.

[0025] The ability of the capacitance element (storage capacitor) is explained. The gate potential of the driving TFT to which the image signals have been inputted is changed by a leak current of transistors or the like, and the source-gate voltage of the driving TFT is changed. As a result, the drain current of the driving TFT is changed, and the luminance is decreased. That is, the capacitance element needs the ability to hold the charge to set the gate potential of the driving TFT

at a constant value or an almost constant value for a predetermined display period.

[0026] The configuration of the present invention is described as below.

[0027] A semiconductor device of the invention is characterized by comprising a pixel having a light emitting element.

[0028] wherein the pixel has first and second switching elements having two states, a conducting state and a non-conducting state, a transistor, a capacitance element, and the light emitting element,

[0029] a video signal is inputted to a first electrode of the first switching element, and a second electrode of the first switching element is electrically connected to a gate electrode of the transistor,

[0030] a first electrode of the transistor is electrically connected to a first electrode of the second switching element and a first electrode of the light emitting element, and a second electrode of the transistor is electrically connected to a first power source,

[0031] a second electrode of the second switching element is electrically connected to a second power source,

[0032] a second electrode of the light emitting element is electrically connected to a third power source, and

[0033] the capacitance element is disposed between the gate electrode and the first electrode of the transistor.

[0034] A semiconductor device of the invention is characterized by comprising a pixel having a light emitting element.

[0035] wherein the pixel has first, second and third switching elements having two states, a conducting state and a non-conducting state, a transistor, a capacitance element, and the light emitting element,

[0036] a video signal is inputted to a first electrode of the first switching element, and a second electrode of the first switching element is electrically connected to a gate electrode of the transistor,

[0037] a first electrode of the transistor is electrically connected to a first electrode of the second switching element and a first electrode of the light emitting element, and a second electrode of the transistor is electrically connected to a first power source,

[0038] a second electrode of the second switching element is electrically connected to a second power source,

[0039] a second electrode of the light emitting element is electrically connected to a third power source,

[0040] the capacitance element is disposed between the gate electrode and the first electrode of the transistor, and

[0041] a first electrode of the third switching element is electrically connected to the gate electrode of the transistor, and a second electrode of the third switching element is electrically connected to any one of the first electrode of the transistor, the second power source, and the third power source.

[0042] A semiconductor device of the invention is characterized by comprising a pixel having a light emitting element

[0043] wherein the pixel has first, second and third switching elements having two states, a conducting state and a non-conducting state, a transistor, a capacitance element, and the light emitting element,

[0044] a video signal is inputted to a first electrode of the first switching element, and a second electrode of the first switching element is electrically connected to a gate electrode of the transistor,

[0045] a first electrode of the transistor is electrically connected to a first electrode of the second switching element and a first electrode of the light emitting element, and a second electrode of the transistor is electrically connected to a first power source,

[0046] a second electrode of the second switching element is electrically connected to a second power source,

[0047] a second electrode of the light emitting element is electrically connected to a third power source,

[0048] the capacitance element is disposed between the gate electrode and the first electrode of the transistor, and

[0049] a first electrode of the third switching element is electrically connected to the first electrode of the light emitting element, and a second electrode of the third switching element is electrically connected to the second power source.

[0050] A semiconductor device of the invention comprising a pixel having a light emitting element,

[0051] wherein the pixel has first, second and third switching having two states, a conducting state and a non-conducting state, a transistor, a capacitance element, and the light emitting element,

[0052] a video signal is inputted to a first electrode of the first switching element, and a second electrode of the first switching element is electrically connected to a gate electrode of the transistor.

[0053] a first electrode of the transistor is electrically connected to a first electrode of the second switching element and a first electrode of the light emitting element, and a second electrode of the transistor is electrically connected to a first power source through the third switching element.

[0054] a second electrode of the second switching element is electrically connected to a second power source,

[0055] a second electrode of the light emitting element is electrically connected to a third power source, and

[0056] the capacitance element is disposed between the gate electrode and the first electrode of the transistor.

[0057] In the semiconductor device of the invention, when a conductivity type of the transistor is an N-channel type, potential  $V_1$  of the first power source, potential  $V_2$  of the second power source and potential  $V_3$  of the third power source can be  $V_1{>}V_2$  and  $V_1{>}V_3$ .

[0058] In the semiconductor device of the invention, the potential  $V_2$  of the second power source and the potential  $V_3$  of the third power source also can be  $V_2 < V_3$ .

[0059] in the semiconductor device of the invention, when a conductivity type of the transistor is a P-channel type, potential  $V_1$  of the first power source, potential  $V_2$  of the second power source, and potential  $V_3$  of the third power source can be  $V_1 < V_2$  and  $V_1 < V_3$ .

[0060] In the semiconductor device of the invention, the potential  $V_2$  of the second power source and the potential  $V_3$  of the third power source also can be  $V_2 > V_3$ .

[0061] A semiconductor device of the invention is characterized by comprising a pixel having a light emitting element,

[0062] wherein the pixel has a source signal line, first and second gate signal lines, a current supply line, first, second, and third transistors, a capacitance element, and the light emitting element,

[0063] a gate electrode of the first transistor is electrically connected to the first gate signal line, a first electrode of the first transistor is electrically connected to a first electrode of the second transistor and a first electrode of the light emitting element, and a second electrode of the first transistor is electrically connected to a first power source having a potential difference with the current supply line each other, or the first or second gate signal line in any one of pixels not including the pixel,

[0064] a gate electrode of the second transistor is electrically connected to a first electrode of the third transistor, and a second electrode of the second transistor is electrically connected to the current supply line,

[0065] a gate electrode of the third transistor is electrically connected to the second gate signal line, and a second electrode of the third transistor is electrically connected to the source signal line,

[0066] a second electrode of the light emitting element is electrically connected to a second power source having a potential difference with the current supply line each other, and

[0067] the capacitance element is disposed between the gate electrode and the first electrode of the second transistor. [0068] A semiconductor device of the invention is characterized by comprising a pixel having a light emitting element,

[0069] wherein the pixel has a source signal line, a gate signal line, a current supply line, first, second, and third transistors, a capacitance element, and the light emitting element.

[0070] a gate electrode of the first transistor is electrically connected to the gate signal line, a first electrode of the first transistor is electrically connected to a first electrode of the second transistor and a first electrode of the light emitting element, and a second electrode of the first transistor is electrically connected to a first power source having a potential difference with the current supply line each other or the gate signal line in any one of pixels not including the pixel,

[0071] a gate electrode of the second transistor is electrically connected to a first electrode of the third transistor, and a second electrode of the second transistor is electrically connected to the current supply line,

[0072] a gate electrode of the third transistor is electrically connected to the gate signal line, and a second electrode of the third transistor is electrically connected to the source signal line,

[0073] a second electrode of the light emitting element is electrically connected to a second power source having a potential difference with the current supply line each other, and

[0074] the capacitance element is disposed between the gate electrode and the first electrode of the second transistor.

[0075] A semiconductor device of the invention is characterized by comprising a pixel having a light emitting element.

[0076] wherein the pixel has a source signal line, first, second and third gate signal lines, a current supply line, first, second, third and fourth transistors, a capacitance element, and the light emitting element,

[0077] a gate electrode of the first transistor is electrically connected to the first gate signal line, a first electrode of the first transistor is electrically connected to a first electrode of the second transistor and a first electrode of the light emitting element, and a second electrode of the first transistor is electrically connected to any one of a first power source having a potential difference with the current supply line each other the first, second and third gate signal lines in any one of pixels not including the pixel, and the second and third gate signal lines in the pixel.

[0078] a gate electrode of the second transistor is electrically connected to a first electrode of the third transistor, and a second electrode of the second transistor is electrically connected to the current supply line,

[0079] a gate electrode of the third transistor is electrically connected to the second gale signal line, and a second electrode of the third transistor is electrically connected to the source signal line,

[0080] a second electrode of the light emitting element is electrically connected to a second power source having a potential difference with the current supply line each other, [0081] the capacitance element is disposed between the gate electrode and the first electrode of the second transistor, and

[0082] a gate electrode of the fourth transistor is electrically connected to the third gate signal line, a first electrode of the fourth transistor is electrically connected to the gate electrode of the second transistor, and a second electrode of the fourth transistor is electrically connected to any one of the first electrode of the second transistor, the first power source, and the second power source.

[0083] A semiconductor device of the invention is characterized by comprising a pixel having a light emitting element,

[0084] wherein the pixel has a source signal line, first and second gate signal lines, a current supply line, first, second, third and fourth transistors, a capacitance element, and the light emitting element

[0085] a gate electrode of the first transistor is electrically connected to the first gate signal line, a first electrode of the first transistor is electrically connected to a first electrode of the second transistor and a first electrode of the light emitting element, and a second electrode of the first transistor is electrically connected to any one of a first power source having a potential difference with the current supply line each other, the first and second gate signal lines in any one of pixels not including the pixel, and the second gate signal line in the pixel,

[0086] a gate electrode of the second transistor is electrically connected to a first electrode of the third transistor, and a second electrode of the second transistor is electrically connected to the current supply line,

[0087] a gate electrode of the third transistor is electrically connected to the first gate signal line, and a second electrode of the third transistor is electrically connected to the source signal line,

[0088] a second electrode of the light emitting element is electrically connected to a second power source having a potential difference with the current supply line each other, [0089] the capacitance element is disposed between the gate electrode and the first electrode of the second transistor, and

[0090] a gate electrode of the fourth transistor is electrically connected to the second gate signal line, a first elec-

trode of the fourth transistor is electrically connected to the gate electrode of the second transistor, and a second electrode of the fourth transistor is electrically connected to any one of the first electrode of the second transistor, the first power source, and the second power source.

[0091] A semiconductor device of the invention is characterized by comprising a pixel having a light emitting element.

[0092] wherein the pixel has a source signal line, first, second and third gate signal lines, a current supply line, first, second, third and fourth transistors, a capacitance element, and the light emitting element,

[0093] a gate electrode of the first transistor is electrically connected to the first gate signal line, a first electrode of the first transistor is electrically connected to a first electrode of the second transistor and a first electrode of the light emitting element, and a second electrode of the first transistor is electrically connected to any one of a first power source having a potential difference with the current supply line each other, the first, second and third gate signal lines in any one of pixels not including the pixel, and the second and third gate signal lines in the pixel,

[0094] a gate electrode of the second transistor is electrically connected to a first electrode of the third transistor, and a second electrode of the second transistor is electrically connected to the current supply line,

[0095] a gate electrode of the third transistor is electrically connected to the second gate signal line, and a second electrode of the third transistor is electrically connected to the source signal line,

[0096] a second electrode of the light emitting element is electrically connected to a second power source having a potential difference with the current supply line each other,

[0097] the capacitance element is disposed between the gate electrode and the fit electrode of the second transistor,

[0098] a gate electrode of the fourth transistor is electrically connected to the third gate signal line, a first electrode of the fourth transistor is electrically connected to the first electrode of the light emitting element, and a second electrode of the fourth transistor is electrically connected to the first power source.

[0099] A semiconductor device is characterized by comprising a pixel having a light emitting element,

[0100] wherein the pixel has a source signal line, first and second gate signal lines, a current supply line, first, second, third and fourth transistors, a capacitance element, and

[0101] the light emitting element, a gate electrode of the first transistor is electrically connected to the first gate signal line, a first electrode of the first transistor is electrically connected to a first electrode of the second transistor and a first electrode of the light emitting element, and a second electrode of the first transistor is electrically connected to any one of a first power source having a potential difference with the current supply line each other, the first, second and third gate signal lines in any one of pixels not including the pixel, and the second and third gate signal lines in the pixel,

[0102] a gate electrode of the second transistor is electrically connected to a first electrode of the third transistor, and a second electrode of the second transistor is electrically connected to the current supply line,

[0103] a gate electrode of the third transistor is electrically connected to the first gate signal line, and a second electrode of the third transistor is electrically connected to the source signal line,

[0104] a second electrode of the light emitting element is electrically connected to a second power source having a potential difference with the current supply line each other, [0105] the capacitance element is disposed between the gate electrode and the first electrode of the second transistor, and

[0106] a gate electrode of the fourth transistor is electrically connected to the second gate signal line, a first electrode of the fourth transistor is electrically connected to the first electrode of the light emitting element, and a second electrode of the fourth transistor is electrically connected to the first power source.

[0107] A semiconductor device of the invention is characterized by comprising a pixel having a light emitting element,

[0108] wherein the pixel has a source signal line, first, second and third gate signal lines, a current supply line, first, second, third and fourth transistors, a capacitance element, and the light emitting element,

[0109] a gate electrode of the first transistor is electrically connected to the first gate signal line, a first electrode of the first transistor is electrically connected to a first electrode of the second transistor and a first electrode of the light emitting element, and a second electrode of the first transistor is electrically connected to any one of a first power source having a potential difference with the current supply line each other, the first, second and third gate signal lines in any one of pixels not including the pixel, and the second and third gate signal lines in the pixel,

[0110] a gate electrode of the second transistor is electrically connected to a first electrode of the third transistor, and a second electrode of the second transistor is electrically connected to the current supply line,

[0111] a gate electrode of the third transistor is electrically connected to the second gate signal line, and a second electrode of the third transistor is electrically connected to the source signal line,

[0112] a second electrode of the light emitting element is electrically connected to a second power source having a potential difference with the current supply line,

[0113] the capacitance element is disposed between the gate electrode and the first electrode of the second transistor, the capacitance element holds voltage between the gate electrode and the first electrode of the second transistor, and [0114] the fourth transistor is disposed between the second electrode of the second transistor and the current supply line, or between the first electrode of the second transistor and the first electrode of the light emitting element, and a gate electrode of the fourth transistor is electrically connected to the third gate signal line.

[0115] A semiconductor device of the invention is characterized by comprising a pixel having a light emitting element,

[0116] wherein the pixel has a source signal line, first and second gate signal lines, a current supply line, first, second, third and fourth transistors, a capacitance element, and the light emitting element,

[0117] a gate electrode of the first transistor is electrically connected to the first gate signal line, a first electrode of the first transistor is electrically connected to a first electrode of

the second transistor and a first electrode of the light emitting element, and a second electrode of the first transistor is electrically connected to any one of a first power source having a potential difference with the current supply line each other, the first and second gate signal lines in any one of pixels not including the pixel, and the second gate signal line in the pixel,

[0118] a gate electrode of the second transistor is electrically connected to a first electrode of the third transistor, and a second electrode of the second transistor is electrically connected to the current supply line,

[0119] a gate electrode of the third transistor is electrically connected to the first gate signal line, and a second electrode of the third transistor is electrically connected to the source signal line,

[0120] a second electrode of the light emitting element is electrically connected to a second power source having a potential difference with the current supply line each other, [0121] the capacitance element is disposed between the gate electrode and the first electrode of the second transistor, the capacitance element holds voltage between the gate electrode and the first electrode of the second transistor, and [0122] the fourth transistor is disposed between the second electrode of the second transistor and the current supply line, or between the first electrode of the second transistor and the first electrode of the light emitting element, and a gate electrode of the fourth transistor is electrically connected to the third gate signal line.

[0123] In a semiconductor device of the invention, the first and third transistors can be the same conductive type.

[0124] In a semiconductor device of the invention, the transistors included in the pixel can be the same conductive type.

**[0125]** In a semiconductor device of the invention, when a conductive type of the second transistor is an N-channel type, potential  $V_1$  of the current supply line, potential  $V_2$  of the first power source, and potential  $V_3$  of the second power source are  $V_i > V_2$  and  $V_1 > V_3$ .

[0126] In a semiconductor device of the invention, when the conductive type of the second transistor is the N-channel type, the potential  $V_2$  of the first power source, and the potential  $V_3$  of the second power source are  $V_2 > V_3$ .

[0127] In a semiconductor device of the invention, when the conductive type of the second transistor is a P-channel type, potential  $V_1$  of the current supply line, potential  $V_2$  of the first power source, and potential  $V_3$  of the second power source are  $V_1 < V_2$  and  $V_1 < V_3$ .

[0128] In a semiconductor device of the invention, when the conductive type of the second transistor is the P-channel type, the potential  $V_2$  of the first power source, and the potential  $V_3$  of the second power source mare  $V_2 < V_3$ .

[0129] A method for driving a semiconductor device of the invention is characterized by that a pixel having a light emitting element is disposed,

[0130] wherein the pixel has first and second switching elements having two states, a conducting state and a non-conducting state, a transistor, a capacitance element, and the light emitting element,

[0131] a video signal is inputted to a first electrode of the first switching element, and a second electrode of the first switching element is electrically connected to a gate electrode of the transistor,

[0132] a first electrode of the transistor is electrically connected to a first electrode of the second switching

element and a first electrode of the light emitting element, and a second electrode of the transistor is electrically connected to a first power source,

[0133] a second electrode of the second switching element is electrically connected to a second power source,

[0134] a second electrode of the light emitting element is electrically connected to a third power source,

[0135] the capacitance element is disposed between the gate electrode and the first electrode of the transistor,

[0136] the method for driving the display device comprising:

[0137] a first step of conducting the first and second switching elements to input the video signal to the gate electrode of the transistor, and fixing potential of the first electrode of the transistor,

[0138] a second step of not conducting the first and second switching elements to allow the gate electrode of the transistor to be in a floating state; and

[0139] a third step of supplying current corresponding to potential applied to the gate electrode of the transistor to the light emitting element to emit light,

[0140] wherein in the third step, the capacitance element holds gate-source voltage of the transistor to allow a potential variation of the first electrode of the transistor to be equal to a potential variation of the gate electrode of the transistor.

[0141] A method for driving a semiconductor device of the invention is characterized by that a pixel having a light emitting element is disposed,

[0142] wherein the pixel has first, second and third switching elements having two states, a conducting state and a non-conducting state, a transistor, a capacitance element, and the light emitting element,

[0143] a video signal is inputted to a first electrode of the first switching element, and a second electrode of the first switching element is electrically connected to a gate electrode of the transistor,

[0144] a first electrode of the transistor is electrically connected to a first electrode of the second switching element and a first electrode of the light emitting element, and a second electrode of the transistor is electrically connected to a first power source,

[0145] a second electrode of the second switching element is electrically connected to a second power source,

[0146] a second electrode of the light emitting element is electrically connected to a third power source,

[0147] the capacitance element is disposed between the gate electrode and the first electrode of the transistor, and

[0148] a first electrode of the third switching element is electrically connected to the gate electrode of the transistor, and a second electrode of the third switching element is electrically connected to any one of the first electrode of the transistor, the second power source, and the third power source.

[0149] the method for driving the display device comprising:

[0150] a first step of conducting the first and second switching elements to input the video signal to the gate electrode of the transistor, and fixing potential of the first electrode of the transistor,

[0151] a second step of not conducting the first and second switching elements to allow the gate electrode of the transistor to be in a floating state;

[0152] a third step of supplying current corresponding to potential applied to the gate electrode of the transistor to the light emitting element to emit light; and

[0153] a fourth step of conducting the third switching element to allow gate-source voltage of the transistor to be equal to or below an absolute value of a threshold voltage, and stopping current supply to the light emitting element,

[0154] wherein in the third step, the capacitance element holds the gate-source voltage of the transistor to allow a potential variation of the first electrode of the transistor to be equal to a potential variation of the gate electrode of the transistor.

[0155] A method for driving a semiconductor device of the invention is characterized by that a pixel having a light emitting element is disposed,

[0156] wherein the pixel has first, second and third switching elements having two states, a conducting state and a non-conducting state, a transistor, a capacitance element, and the light emitting element,

[0157] a video signal is inputted to a first electrode of the first switching element, and a second electrode of the first switching element is electrically connected to a gate electrode of the transistor.

[0158] a first electrode of the transistor is electrically connected to a first electrode of the second switching element and a first electrode of the light emitting element, and a second electrode of the transistor is electrically connected to a first power source,

[0159] a second electrode of the second switching element is electrically connected to a second power source,

[0160] a second electrode of the light emitting element is electrically connected to a third power source,

[0161] the capacitance element is disposed between the gate electrode and the first electrode of the transistor, and [0162] a first electrode of the third switching element is electrically connected to the first electrode of the light emitting element, and a second electrode of the third switching element is electrically connected to the second power

[0163] the method for driving the display device comprising:

source.

[0164] a first step of conducting the first and second switching elements to input the video signal to the gate electrode of the transistor, and fixing potential of the first electrode of the transistor:

[0165] a second step of not conducting the first and second switching elements to allow the gate electrode of the transistor to be in a floating state;

[0166] a third step of supplying current corresponding to potential applied to the gate electrode of the transistor to the light emitting element to emit light; and

[0167] a fourth step of conducting the third switching element to allow gate-source voltage of the transistor to be equal to or below an absolute value of a threshold voltage, and stopping current supply to the light emitting element,

[0168] wherein in the third step, the capacitance element holds the gate-source voltage of the transistor to allow a potential variation of the first electrode of the transistor to be equal to a potential variation of the gate electrode of the transistor.

[0169] A method for driving a semiconductor device of the invention is characterized by that a pixel having a light emitting element is disposed,

[0170] wherein the pixel has first, second, and third switching elements having two states, a conducting state and a non-conducting state, a transistor, a capacitance element, and the light emitting element,

[0171] a video signal is inputted to a first electrode of the first switching element, and a second electrode of the first switching element is electrically connected to a gate electrode of the transistor.

[0172] a first electrode of the transistor is electrically connected to a first electrode of the second switching element and a first electrode of the light emitting element, and a second electrode of the transistor is electrically connected to a first power source through the third switching element

[0173] a second electrode of the second switching element is electrically connected to a second power source,

[0174] a second electrode of the light emitting element is electrically connected to a third power source, and

[0175] the capacitance element is disposed between the gate electrode and the first electrode of the transistor,

[0176] the method for driving the display device comprising:

[0177] a first step of conducting the first and second switching elements to input the video signal to the gate electrode of the transistor, and fixing potential of the first electrode of the transistor:

[0178] a second step of not conducting the first and second switching elements to allow the gate electrode of the transistor to be in a floating state;

[0179] a third step of conducting the third switching element to supply current corresponding to potential applied to the gate electrode of the transistor to the light emitting element to emit light; and

[0180] a fourth step of not conducting the third switching element and stopping current supply to the light emitting element,

[0181] wherein in the third step, the capacitance element holds gate-source voltage of the transistor to allow a potential variation of the first electrode of the transistor to be equal to a potential variation of the gate electrode of the transistor.

#### BRIEF DESCRIPTION OF E DRAWINGS

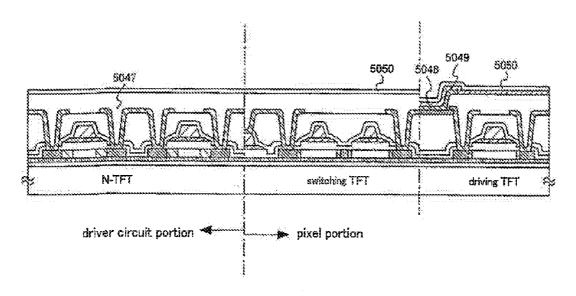

[0182] FIGS. 1A and 1B are diagrams for illustrating an embodiment of the invention and the operation;

[0183] FIGS. 2A to 2D are diagrams for illustrating the operation in the case of forming the TFTs to be unipolar by the traditional configuration;

[0184] FIGS. 3A to 3C are diagrams for illustrating the operation of the circuit as according to the configuration shown in FIG. 1A;

[0185] FIGS. 4A to 4C are diagrams for illustrating an embodiment of the invention and the operation;

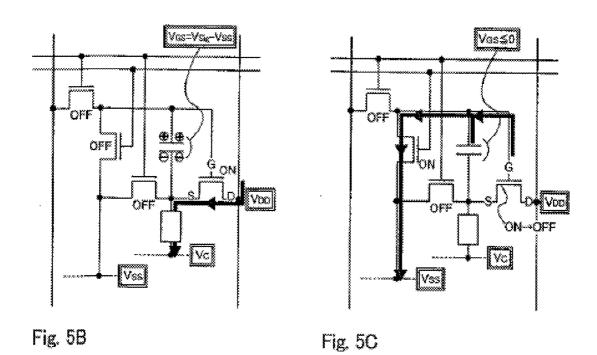

[0186] FIGS. 5A to 5C are diagrams for illustrating an embodiment of the invention and the operation;

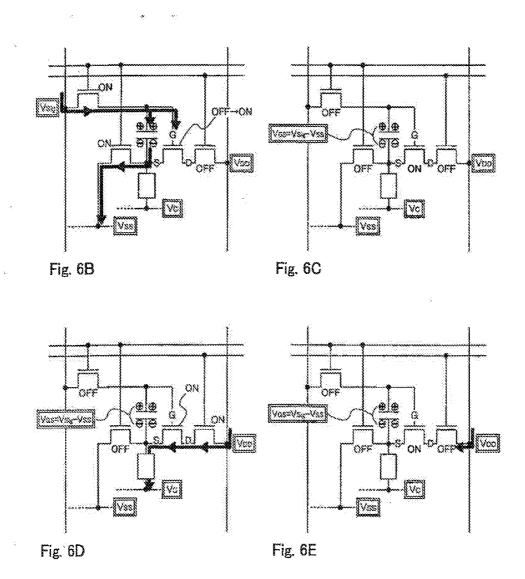

[0187] FIGS. 6A to 6E are diagrams for illustrating an embodiment of the invention and the operation;

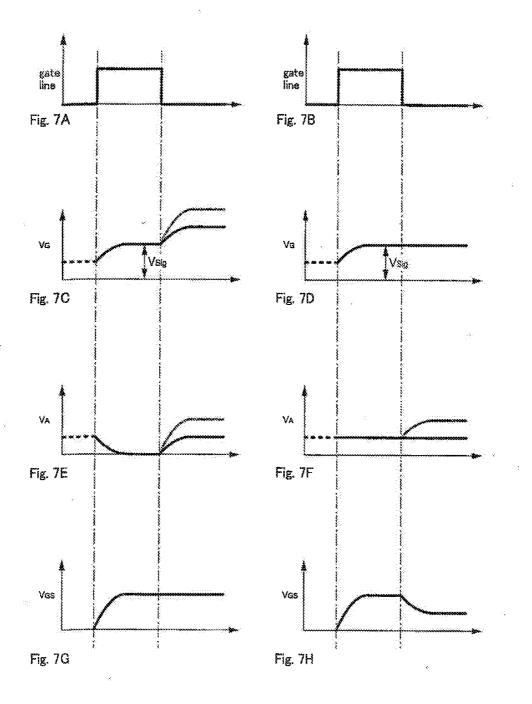

[0188] FIGS. 7A to 7H are diagrams comparing the invention with the traditional example on the change in the potential around the gate electrode and the source region of the driving TFT;

[0189] FIG. 8 is a diagram introducing one example of the pixel configured of the unipolar TFTs;

[0190] FIG. 9 is a diagram depicting an embodiment of the invention;

[0191] FIGS. 10A and 10B are diagrams for illustrating the time gray scale system;

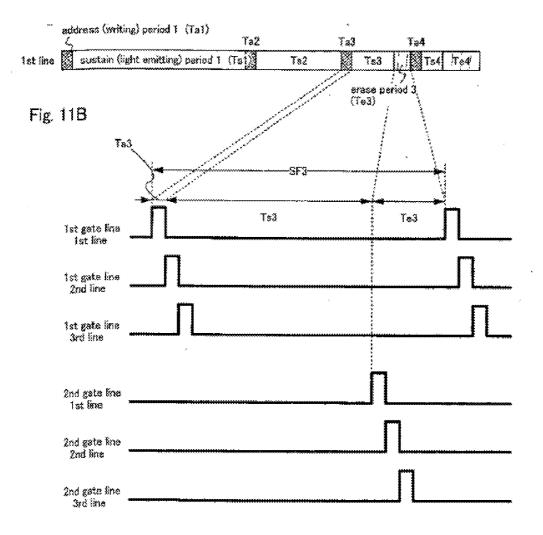

[0192] FIGS. 1A to 11C are diagrams for illustrating the time gray scale system;

[0193] FIGS. 12A to 12D are diagrams for illustrating an embodiment of the invention and the operation;

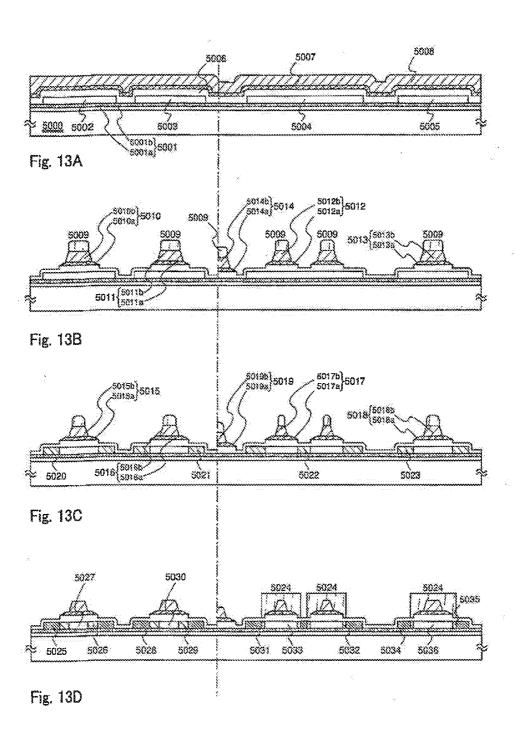

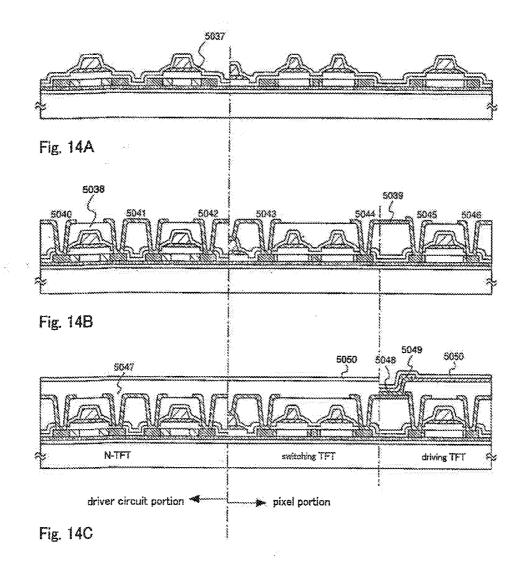

[0194] FIGS. 13A to 13D are diagrams for illustrating the fabrication processes of a semiconductor device;

[0195] FIGS. 14A to 14C are diagrams for illustrating the fabrication processes of the semiconductor device;

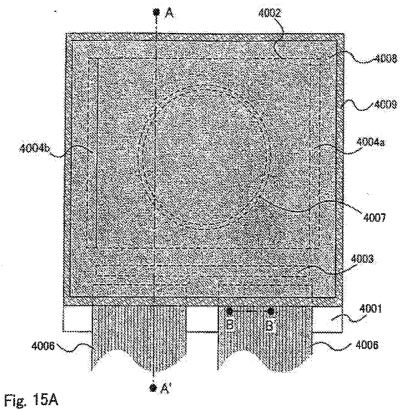

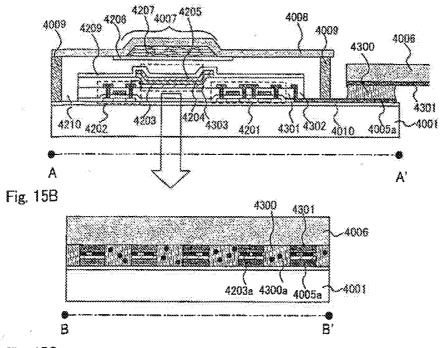

[0196] FIGS. 15A to 15C are a top view and cross sections of the semiconductor device;

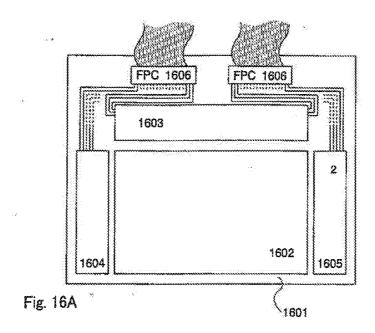

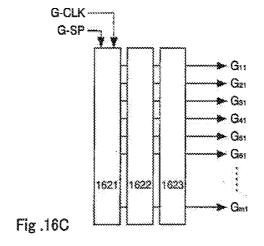

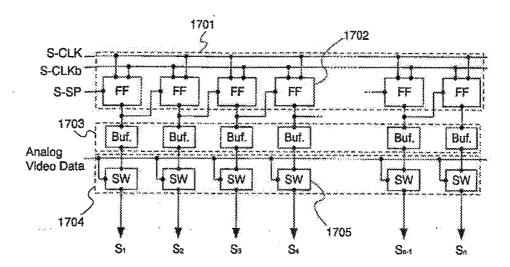

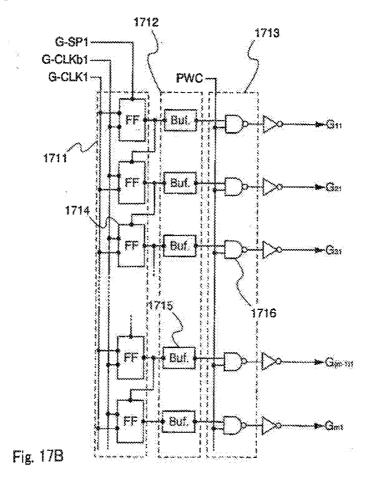

[0197] FIGS. 16A to 16C are diagrams depicting the configuration of a semiconductor device for display with analogue video signals;

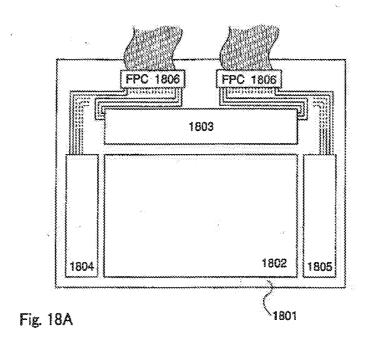

[0198] FIGS. 17A and 17B are diagrams depicting an example of a source signal line drive circuit and a gate signal line drive circuit in the device shown in FIGS. 16A to 16C; [0199] FIGS. 18A and 18B are diagrams depicting the configuration of a semiconductor device for display with digital video signals;

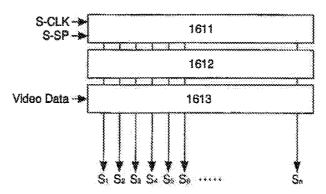

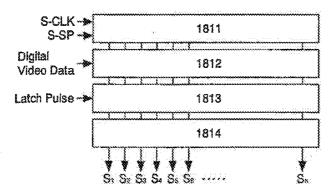

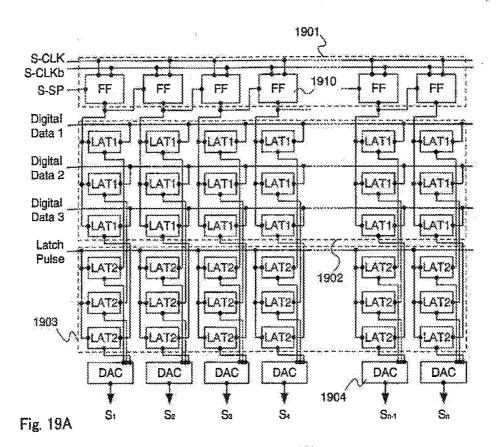

[0200] FIGS. 19A and 19B are diagrams depicting an example of a source signal line as drive circuit in the device shown in FIGS. 18A and 18B;

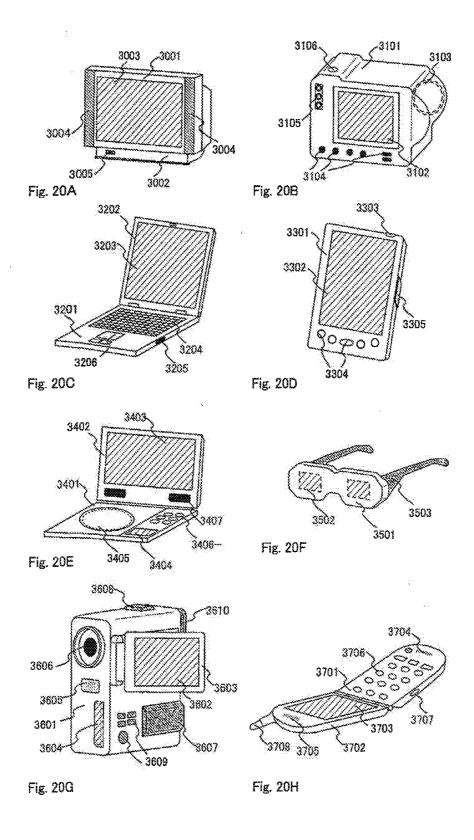

[0201] FIGS. 20A to 20H are diagrams depicting examples of electronic devices applicable to the invention; [0202] FIGS. 21A to 21C are diagrams for illustrating an embodiment of the invention and the operation; and

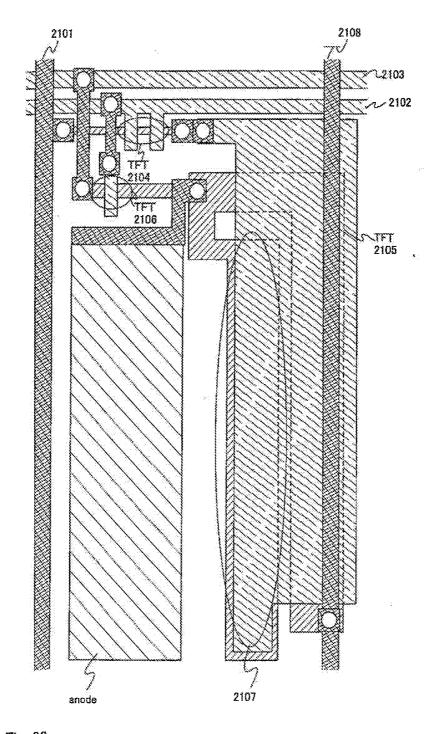

[0203] FIG. 22 is a diagram depicting a top view of the pixel configuration of the invention.

# DESCRIPTION OF THE PREFERRED EMBODIMENT

#### Embodiment 1

[0204] FIG. 1A depicts an embodiment of the invention. The pixel of the invention has a source signal line 101, a gate signal line 102, first, second and third TFTs 103 to 105, a capacitance element 106, a current supply line 107, an EL element 108, and power source lines 109 and 110. The gate electrode of the TFT 103 is connected to the gate signal line 102, the first electrode of the TFT 103 is connected to the source signal line 101, and the second electrode of the TFT 103 is connected to the gate electrode of the TFT 104. The first electrode of the TFT 104 is connected to the current supply line 107, and the second electrode of the TFT 104 is connected to the first electrode of the TFT 105 and the first electrode of the EL element. The gate electrode of the TFT 105 is connected to the gate signal line 102, and the second electrode of the TFT 105 is connected to the power source line 110. The second electrode of the EL element 108 is connected to the power source line 109. The capacitance element 106 is disposed between the gate electrode and the second electrode of the TFT 104, holding the gate-source voltage.

[0205] Now, all the TFTs 103 to 105 are the N-channel TFT, and they are to be turned on when the gate-source voltage exceeds the threshold. In addition, in the EL element 108, the first electrode is the anode, and the second electrode is cathode. The anode potential is set  $V_A$ , and the cathode potential, i.e. the potential of the power source line 109 is set  $V_C$ . Furthermore, the potential of the current supply line 107 is set  $V_{DD}$ , and the potential of the power source line 110 is set  $V_{SS}$ . The potential of the video signal is set  $V_{SS}$ .

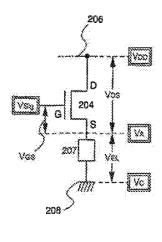

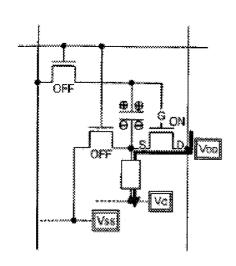

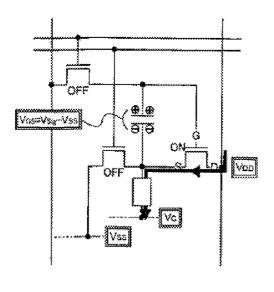

[0206] The operation of the circuit will be described with FIGS. 1A, 1B and 3A to 3C. Here, the gate (G), the source (S), and the drain (D) of the TFT 104 is defined as shown in FIG. 3A.

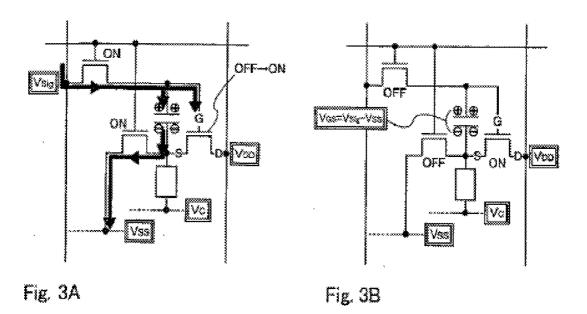

[0207] The gate signal line 102 is selected in a certain pixel to turn on the TFTs 103 and 105. As shown in FIG. 3A, video signals are inputted to the gate electrode of the TFT 104 from the source signal line 101, and the potential is turned to be  $V_{Sig}$ . In the meantime, the TFT 105 is on, thus being  $V_A = V_{SS}$ . At this time, when  $V_{SS} \leq V_C$  is set, current is not carried through the EL element 108 in writing the video signals. However,  $V_{SS} > V_C$  is set, and thus it is acceptable to carry current through the EL element 108. The essence here is that  $V_A$  is fixed to a fixed potential. According to this operation, the voltage between both electrodes of the capacitance element 106 is turned to be  $(V_{Sig} - V_{SS})$ . Then, when the select period of the gate signal line 102 is finished and the TFTs 103 and 105 are turned off the migration path of charges stored in the capacitance element 106 is gone, and the gate-source voltage  $(V_{Sig} - V_{SS})$  of the TFT 104 is held (FIG. 3B).

[0208] Here, when  $(V_{Sig}-V_{SS})$  exceeds the threshold of the TFT 104, the TFT 104 is turned on, current is started to carry through the EL element from the current supply line 107, and light emission is started (FIG. 3C), increasing the source potential of the TFT 104. At this period, the gate electrode of the TFT 104 is in the floating state, and the capacitance element 106 holds the gate-source voltage of the TFT 104. Thus, the potential of the gate electrode is increased with the rise in the source potential. At this period, the capacitance component exists between the gate electrode and the semiconductor layer (in the source region or drain region) in the TFTs 104 and 105, but the capacitance value of the capacitance element 106 is set to be dominant sufficiently over the capacitance component, whereby the rise in the source potential of the TFT 104 is made nearly equal to the rise in the gate potential of the TFT 104.

[0209] Based on the operation, the operation according to the deteriorated EL element or not will be considered with FIG. 1B. FIG. 1B schematically depicts that 151 is the potential of the gate signal line 102, 152 and 153 are the potential  $V_G$  of the gate electrode of the TFT 104, 154 and 155 are the anode potential  $V_A$  of the EL element 108, i.e. the source potential of the TFT 104, and 156 is the gate-source voltage  $V_{GS}$  of the TFT 104.

[0210] Now, in the section expressed by i shown in FIG. 1B, the gate signal line 102 is selected to be at high level. Therefore, video signals are written in this section, and the gate potential  $V_G$  of the TFT 104 rises. In the meantime, the TFT 105 is on, and thus the anode potential  $V_A$  of the EL element 108, i.e. the source potential of the TFT 104 becomes equal to  $V_{SS}$ . Thus, the gate-source voltage  $V_{GS}$  of the TFT 104 becomes larger. Furthermore, when it is  $V_A = V_{SS} < V_C$  in the section, the EL element 108 does not emit light regardless of the value of the video signal  $V_{Sig}$ . [0211] In the timing expressed by ii, the selection of the gate signal line 102 is finished to be at low level, and the TFTs 103 and 105 are turned off.  $V_{GS} = (V_{Sig} - V_A)$  at this time is held in the capacitance element 106.

[0212] Subsequently, go into the section expressed by iii, and the light emission is started. At this time, when the gate-source voltage  $V_{GS}$  of the TFT 104 exceeds the threshold, the TFT 104 is turned on to carry the drain current, and the EL element 108 emits light. At the same time, the source

potential of the TFT 104 also rises. Here, as described above, the gate electrode of the TFT 104 is in the floating state, and thus the potential rises as similar to the rise in the source potential of the TFT 104.

[0213] Here, the case where the EL element 108 has been deteriorated will be considered. When the EL element is deteriorated, anode-cathode voltage becomes large in carrying a current of a certain value through the EL element 108 as described above. Thus,  $V_A$  rises as expressed by 155. However, in the invention,  $V_G$  also rises by the rise of  $V_A$ , and consequently, it is revealed that  $V_{GS}$  is not changed.

[0214] On the other hand, as shown in FIGS. 7A to 7H, in the case of the traditional configuration shown in FIG. 21, when video signals are once inputted and the potential is turned to be  $V_{Sig}$ , the gate potential  $V_G$  of the TFT 204 is not changed after that. Therefore, the EL element 207 is deteriorated and  $V_A$  rises, the gate-source voltage of the TFT 204 becomes smaller than before deteriorated (FIGS. 7G and 7H). In such the case, even though the TFT 204 is operated in the saturation region, the current value at the operating point is to be changed. Accordingly, when the EL element 207 is deteriorated and the voltage-current characteristics are changed, the current carried through the EL element 207 becomes smaller to cause the luminance to be decreased.

[0215] As described above, the current value is not changed even in the deterioration of the EL element, whereby the invention can eliminate the influence of the deterioration of the EL element.

**[0216]** In addition, both the potential  $V_{SS}$  and  $V_C$  of the power source lines can be set arbitrarily. Therefore,  $V_{SS} < V_C$  is set, whereby the reverse bias can be easily applied to the EL element.

[0217] Furthermore, TFTs 103 and 105 are fine to simply function as the switching element, and thus the polarity is not defined. More specifically, even though all the TFTs configuring the pixel are set to be unipolar, the normal operation is feasible. In FIG. 1A, the TFTs 103 and 105 are set to have the same polarity and are controlled only by the gate signal line 102. However, it is acceptable that first and second gate signal lines different from each other are used to control the separate TFTs. In this cue, the TFTs 103 and 105 may have the different polarity each other. However, in consideration of the numerical aperture of the pixel, the number of lines for wiring is desired to be a smaller number as much as possible.

#### Embodiment 2

[0218] According to the configuration shown in FIG. 1A, for the lines routed to the pixel part, five lines were needed: the source signal line, the gate signal line, the current supply line  $(V_{DD})$ , the power source line  $(V_C)$ , and the power source line  $(V_{SS})$ . In this embodiment, the configuration will be described in which lines for wiring are shared, whereby allowing the number of lines for wiring per pixel to be reduced and high numerical aperture to be obtained.

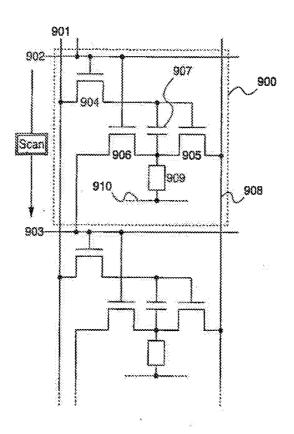

[0219] FIG. 9 depicts the configuration of the embodiment. The point different from the embodiment 1 is only the point in that the second electrode of a TFT 906 is connected to the power source line  $(V_{SS})$  but it is connected to the gate signal line in a pixel of the next row in the embodiment. Suppose the pixel expressed by a dotted frame 900 is in the ith row, the second electrode of the TFT 906 is connected to the gate signal line in the i+1st row.

**[0220]** As the pulse condition of selecting the gate signal line, it is acceptable that the gate-source voltage of the TFT **904** sufficiently exceeds the threshold at high level. More specifically, it is acceptable that the potential is sufficiently larger than the threshold to the maximum value of the video signal  $V_{Sig}$ . In the meantime, the potential is fine to surely turn off the TFT **904** at low level. Accordingly, the potential at low level is set equal to  $V_{SS}$  in the gate signal line.

[0221] When the ith gate signal line is selected to be at high level and the TFTs 904 and 906 are turned on, the i+1st gate signal line is not selected yet. More specifically, it is at low level and the potential is  $V_{SS}$ . Therefore, the anode potential  $V_A$  of the EL element becomes equal to  $V_{SS}$  through the TFT 906 as similar to the embodiment. Accordingly, when the lines for wiring are shared in accordance with the embodiment, the same effect as the embodiment 1 can be attained.

[0222] In addition, where to connect the second electrode of the TFT 906 is not limited to the i+1st gate signal line, when it is a position where a fixed potential  $V_{SS}$  can be applied while the ith gate signal line is selected to be at high level and the TFT 906 is on. For example, it may be the i-1st gate signal line or other than this. When the signal lines in the adjacent rows are shared, the pulse of the signal lines are desired not to be overlapped each other.

[0223] Furthermore, as described in the embodiment 1, the TFTs 904 and 906 are fine to simply function as the switching elements. Thus, the polarity is not defined, which is not limited to being controlled by a single gate signal line 902 as shown in FIG. 9.

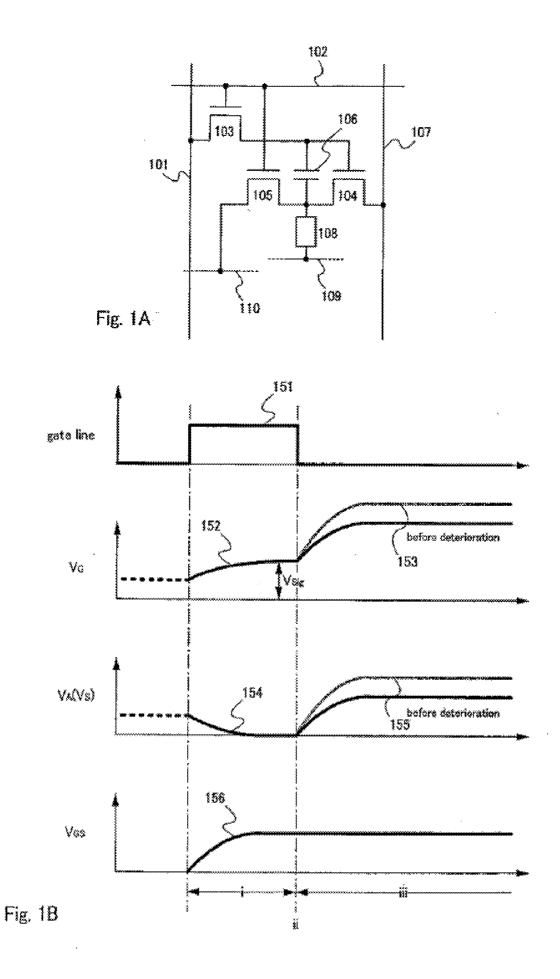

#### Embodiment 3

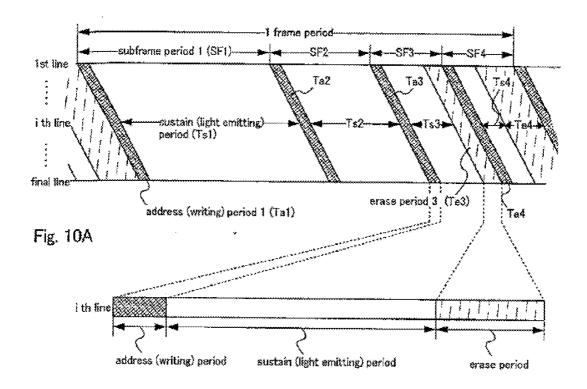

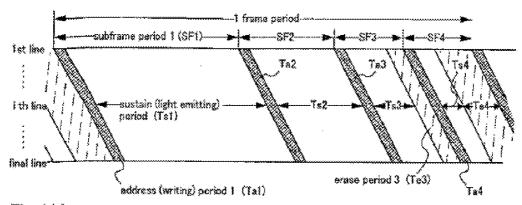

[0224] It is called the analogue gray scale system that the gate-source voltage of a driving TFT is controlled, and the current value carried through an EL element is controlled by analogue quantity for display. In the meantime, the digital gray scale system is proposed in which an EL element is driven only by two states, a hundred or zero percent luminance. In this system, only two levels of gray scale, black and white, can be displayed, but it has a merit of hardly being subject to variations in the TFT characteristics. To intend to have the multiple gray scale by the digital gray scale system, a driving method of combining with the time gray scale system is used. The time gray scale system is the method of expressing the gray scale by the length of time that the element emits light for a long time or short time. [0225] When the digital gray scale system is combined with the time gray scale system, one frame period is split into a plurality of subframe periods as shown in FIG. 10A. Each subframe period has the address (writing) period, the sustain (light emission) period, and the erase period, as shown in FIG. 10B. The gray scale is expressed in which the subframe periods corresponding to the bit numbers for display are disposed, the length of the sustain (light emission) period is set to  $2^{(n-1)}:2^{(n-2)}:\ldots:2:1$  in each subframe period, the EL element is selected to emit light or not to emit light in each sustain (light emission) period, and the difference in the length of the total time while the EL element is emitting light is utilized. The luminance is high when the time for emitting light is long, whereas the luminance is low when short. In addition, FIGS. 10A and 10B depict the example of four bit gray scale in which one frame period is split into four subframe periods and 2<sup>4</sup>=16 levels of gray scale can be expressed by the combination of the sustain

(light emission) periods. Furthermore, the gray scale can be expressed without particularly setting the ratio of the length of the sustain periods to be the ratio of the powers of two. Moreover, a certain subframe period may be further split. [0226] When the multiple gay scale is intended with the time gray scale system, the length of the sustain (light emission) period of lower bits becomes further shorter. Therefore, when the subsequent address period is to start immediately after the sustain (light emission) period is finished, the period of overlapping with the address (writing) periods of the different subframe periods is generated. In this case, video signals inputted to a certain pixel are also inputted to the different pixel at the same time, and thus the normal display cannot be performed. The erase period is disposed for solving such the problem. As shown in FIG. 10B, it is disposed after Ts3 and Ts4 so as not to overlap two different address (writing) periods with each other. Accordingly, the erase period is not disposed in SF1 and SF2 where the sustain (light emission) period is long enough and the two different address (writing) periods will not overlap with

[0227] In this manner, to drive the EL element by the method of combining the digital gray scale system with the time gray scale system, there might be the case of adding the operation that the light emission of the EL element is forcedly stopped and the erase period is disposed.

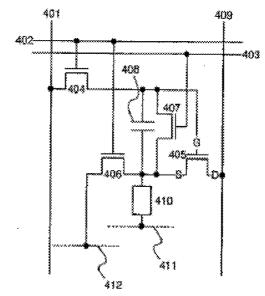

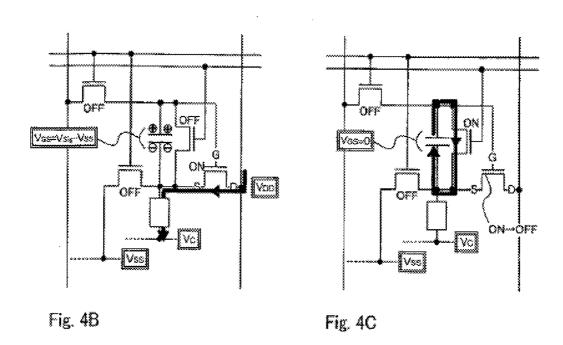

[0228] FIG. 4A depicts an example of adding a second gate signal line 403 and an erasing TFT 407 to the pixel having the configuration shown in the embodiment 1 to respond to the driving method of combining the digital gray scale system with the time gray scale system. The gate electrode of the erasing TFT 407 is connected to the second gate signal line 403, the first electrode of the erasing TFT 407 is connected to the gate electrode of a TFT 405 and the first electrode of a capacitance element 408, and the second electrode of the erasing TFT 407 is connected to the second electrode of the TFT 405 and the second electrode of the TFT 405 and the second electrode of the TFT 405 and the second electrode of the capacitance element 408.

**[0229]** The operation that a first gate signal line **402** is selected to input video signals is the same as that shown in the embodiment 1, thus omitting it here. In addition, during the input of the video signals, the second gate signal line is at low level and the erasing TFT **407** is off. At this time,  $V_{Sig}$  takes either the potential to surely turn on the TFT **405** or potential to turn off the TFT **405**.

[0230] Here, the operation from the sustain (light emission) period to the erase period will be describe with FIGS. 4A to 4C and 11A to 11C. FIG. 1A is the same as that shown in FIG. 10A. As shown in FIG. 11B, one frame period has four subframe periods. In subframe periods SF3 and SF4 having a short sustain (light emission) period, they have erase periods Te3 and Te4, respectively. Here, the operation in SF3 will be exemplified for description.

[0231] After the video signals are finished to input, the current corresponding to the gate-source voltage  $V_{GS}$  of the TFT 405 is carried through an EL element 410 to emit light, as shown in FIG. 10B. Then, when timing is reached to finish the sustain (light emission) period, pulses are inputted to the second gate signal line 403 to be at high level, and the erasing TFT 407 is turned on to set the gate-source voltage  $V_{GS}$  of the TFT 405 to be zero, as shown in FIG. 4C. Accordingly, the TFT 405 is turned off, the current to the EL element 410 is broken, and the EL element 410 forcedly stops light emission.

[0232] The operation is shown in FIG. 11C as a timing chart. The erase period Te3 is the period that after the sustain (light emission) period Ts3, a pulse is inputted to the second gate signal line 403, the EL element 410 stops light emission, and then a pulse is again inputted to the first gate signal line 402 to start inputting the next video signal.

[0233] In addition, in the configuration shown in FIG. 4A, the second electrode of a TFT 406 is connected to a power source line 412, but the power source line 412 can be substituted by the gate signal line in the adjacent row as shown in the embodiment 2. Furthermore, in the embodiment, the second gate signal line 403 is disposed for controlling the erasing TFT 407, and thus the second electrode of the TFT 406 may be connected to the second gate signal line 403.

[0234] Although the TFTs 404 and 406 are controlled by the gate signal line 402, a new gate signal line may be added. In this case, the TFTs 404 and 406 can be controlled by the gate signal line 402 and the newly added gate signal line, respectively.

#### Embodiment 4

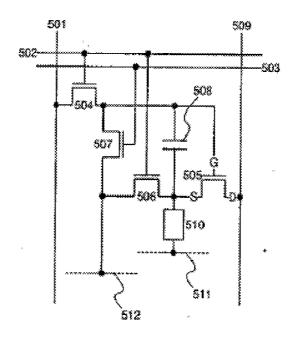

[0235] FIG. 5A depicts an example of disposing the erasing TFT at the position different from that shown in the embodiment 3. In this embodiment, an erasing TFT 507 is disposed between the gate electrode of a TFT 505 to the first electrode of a capacitance element 508 and a power source line 512.

[0236] The driving method is acceptable to be conducted by the method of combining the digital gray scale with the time gray scale system regarding from the input of video signals to light emission as similar to the embodiment 3. Thus, the description is omitted here, and the operation in the erase period will be described.

[0237] When timing is reached to finish the sustain (light emission) period, a pulse is inputted to a second gate signal line 503 to be at high level, the erasing TFT 507 is turned on, and the potential of the gate electrode of the TFT 505 is turned to be  $V_{SS}$ , as shown in FIG. 5C. More specifically, in the erase period, the gate-source voltage  $V_{GS}$  of the TFT 505 is fine to be set below the threshold.

[0238] The source potential of the TFT 505 is in the potential at least equal to or greater than  $V_{SS}$ . Therefore, the operation of the erasing TFT 507 allows the gate-source voltage  $V_{GS}$  of the TFT 505 to be  $V_{GS} \le 0$ , and the TFT 505 is turned off. Accordingly, the erase period is the period that the EL element 510 stops light emission, a pulse is again inputted to a first gate signal line 502, and the next video signal is again started to input.

[0239] In addition, in the configuration shown in FIG. 5A, the second electrode of a TFT 506 is connected to the power source line 512, but the power source line 512 can be substituted by the gate signal line in the adjacent row as shown in the embodiment 2. Furthermore, in the embodiment, the second gate signal line 503 is disposed for controlling the erasing TFT 507. Thus, the second electrode of the TFT 506 may be connected to the second gate signal line 503.

[0240] Although the TFTs 504 and 506 are controlled by the gate signal line 502, a new gate signal line may be added. In this case, the TFTs 504 and 506 can be controlled by the gate signal line 402 and the newly added gate signal line, respectively.

#### Embodiment 5

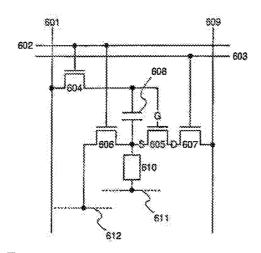

[0241] FIG. 6A depicts an example of disposing the erasing TFT at the position different from that shown in the embodiments 3 and 4. In this embodiment, an erasing TFT 607 is disposed between the first electrode of a TFT 605 and a current supply line.

[0242] The operation of the circuit will be described. A first gate signal line 602 is selected to be at high level, a TFT 604 is turned on, and video signals are inputted to a pixel from a source signal line 601. In the meantime, a TFT 606 is also turned on to allow the anode potential  $V_A$  of an EL element 610 to be equal to  $V_{SS}$ . At this time, when  $V_{SS} \leq V_C$  is set, current is not carried though the EL element 610 in writing the video signals, and thus the TFT 607 is fine to be on or off.

[0243] When the input of video signals is finished and the first gate signal line 602 is not selected, the gate electrode of the TFT 605 is in the floating state and the migration path for stored charges is blocked in a capacitance element 608. Thus, the gate-source voltage  $V_{GS}$  is held in the capacitance element 608.

[0244] Subsequently, a second gate signal line 603 is selected to be at high level and the TFT 607 is turned on, whereby current is carried as shown in FIG. 6D, the anode potential  ${\rm V}_A$  of the EL element 610 rises to generate the potential difference with the cathode potential  ${\rm V}_C$ , and the current is carried to emit light. In addition, it is acceptable that the TFT 607 is turned on from the state of inputting the video signals. In this case, at the moment that the first gate signal line 602 is turned not to be selected, current is supplied to the EL element 610 through the TFTs 607 and 605, and the anode potential  ${\rm V}_A$  of the EL element 610 rises to generate the potential difference with the cathode potential  ${\rm V}_C$ , carrying the current to emit light.

[0245] When timing is reached to finish the sustain (light emission) period, the second gate signal line 603 is not selected to be at low level, the TFT 607 is turned off, and the current path from a current supply line 609 to the EL element 610 is blocked. Accordingly, the current is not carried through the EL element 610 to stop light emission. After that, the erase period is the period that a pulse is again inputted to the first gate signal line 602 and the next video signal is started to input.

[0246] In addition, the TFT 607 is fine to be disposed between the first electrode of the TFT 605 and the anode of the EL element 610. More specifically, it is acceptable that the TFT 607 is disposed in the current path between the current supply line 609 and the EL element 610 and the current supply to the EL element 610 can be cut during the erase period.

[0247] Although the TFTs 604 and 606 are controlled by the gate signal line 602, a new gate signal line may be added. In this case, the TFTs 604 and 606 can be controlled by the gate signal line 602 and the newly added gate signal line, respectively.

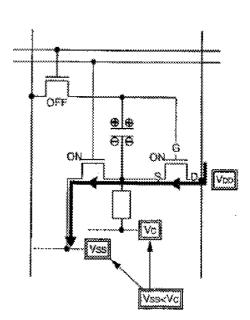

#### Embodiment 6

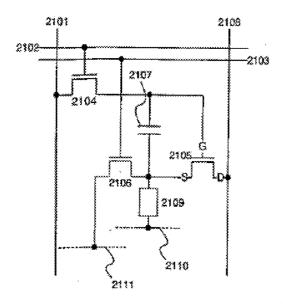

[0248] In the embodiments 3 to 5, the example of adding the TFT to dispose the erase period has been described, but in this embodiment, an example of performing the same operation will be described without adding the erasing TFT. [0249] FIG. 21A depicts the configuration. The configuration is nearly similar to that shown in the embodiment 1,

but the difference is in that TFTs 2104 and 2106 are controlled by separate gate signal lines 2102 and 2103, respectively.

[0250] As shown in FIG. 21B, in the sustain (light emission) period, a capacitance element 2107 fixes the gate-source voltage of a TFT 2105 and the current accompanying this is carried through an EL element 2109 to emit light.

[0251] Subsequently, go to the erase period, and a pulse is inputted to the second gate signal line 2103 to turn on the TFT 2106. At this time, the potential of a power source line 2111 connected to the second electrode of the TFT 2106 is set lower than the cathode potential of the EL element 2109, i.e. the potential of a power source line 2110, whereby current is not carried through the EL element 2109. Accordingly, the current at this time is carried as shown in FIG. 21C.

[0252] In addition, the gate signal line in the adjacent row may be used for the power source line 2111 as described in the other embodiments.

#### Embodiment 7

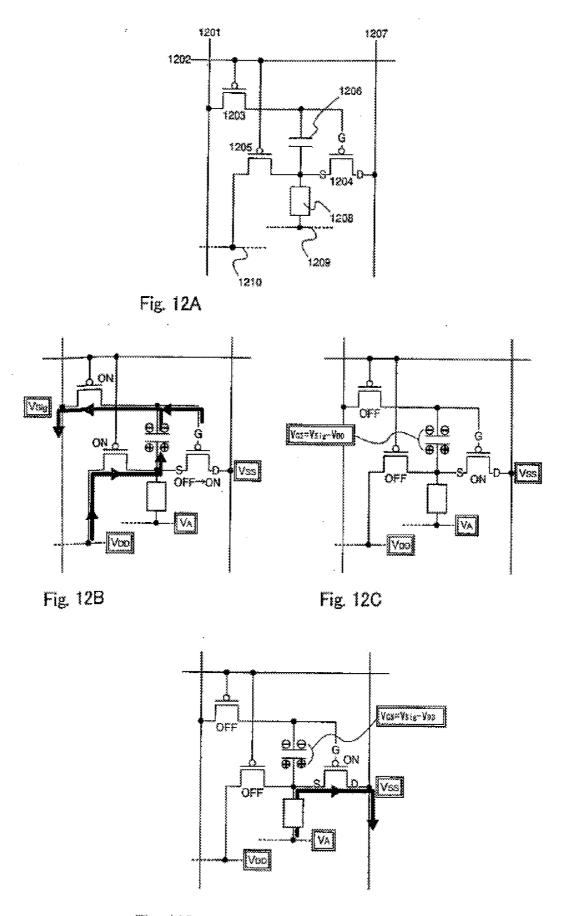

[0253] The N-channel TFT has been used for the TFT for supplying current to the EL element. However, the invention can be implemented by using the P-channel TFT for the driving TFT. FIG. 12A depicts the exemplary configuration. [0254] The circuit configuration is the same as that using the N-channel TFT shown in FIG. 1A. However, the differences are in that the configuration of an EL element 1208 is reverse, one side connected to the second electrode of the TFT 1204 is the cathode, and the other side connected to a power source line 1209 is the anode, and that the potential of a current supply line 1207 is  $V_{SS}$ , the potential of a power source line 1209 is  $V_{A}$ , and the potential of a power source line 1210 is  $V_{DD}$ . Here, it is  $V_{SS} < V_{DD}$  and  $V_{A} < V_{DD}$ .

[0255] The operation of the circuit will be described with FIGS. 12B to 12D. In addition, the polarity of the TFTs is the P-channel type, a low level is inputted to the gate electrode to turn on the TFTs, and a high level is inputted to turn off the TFTs.

[0256] In a certain row, a gate signal line 1202 is selected to be at low level, and TFTs 1203 and 1205 are turned on. As shown in FIG. 12B, video signals are inputted to the gate electrode of the TFT 1204 from a source signal line 1201, and the potential is turned to be  $V_{SS}$ . In the meantime, the TFT 1205 is on, and thus the cathode potential  $V_C$  of the EL element 1208 is turned to be  $V_C = V_{DD}$ . At this time, when  $V_A \ge V_{DD}$  is set, current is not carried through the EL element 1208 in writing the video signals. According to this operation, the voltage between both electrodes of a capacitance element 1206, that is, the gate-source voltage of the TFT **1204** is turned to be  $(V_{Sig}-V_{DD})$ . Then, when the select period of the gate signal line **1202** is finished to be at high level and the TFTs 1203 and 1205 are turned off, the migration path for charges stored in the capacitance element 1206 is gone and the gate-source voltage  $(V_{\textit{Sig}} - V_{\textit{DD}})$  of the TFT 1204 is held (FIG. 12C).

[0257] Here, when  $(V_{Sig}-V_{DD})$  is below the threshold of the TFT 1204, the TFT 1204 is turned on, current is carried through the power source line 1209, the EL element 1208 and the current supply line 1207 to start light emission (FIG. 12D), and the source potential of the TFT 1204 drops. At this time, the gate electrode of the TFT 1204 is in the floating state, and the capacitance element 1206 holds the gate-

source voltage of the TFT 1204. Therefore, the potential of the gate electrode also drops with the decrease in the source potential.